Scientists at a leading research institution have unveiled what they describe as the “most accurate” quantum computing chip ever built, using a new silicon-based computing architecture that sharply cuts error rates in quantum operations. By marrying conventional silicon fabrication with carefully engineered quantum behavior, the team reports unprecedented fidelity in qubit performance that could accelerate real-world quantum computation and simulation. The result is a prototype that moves quantum hardware closer to scalable, commercially relevant systems rather than fragile laboratory demonstrations.

The New Silicon-Based Architecture

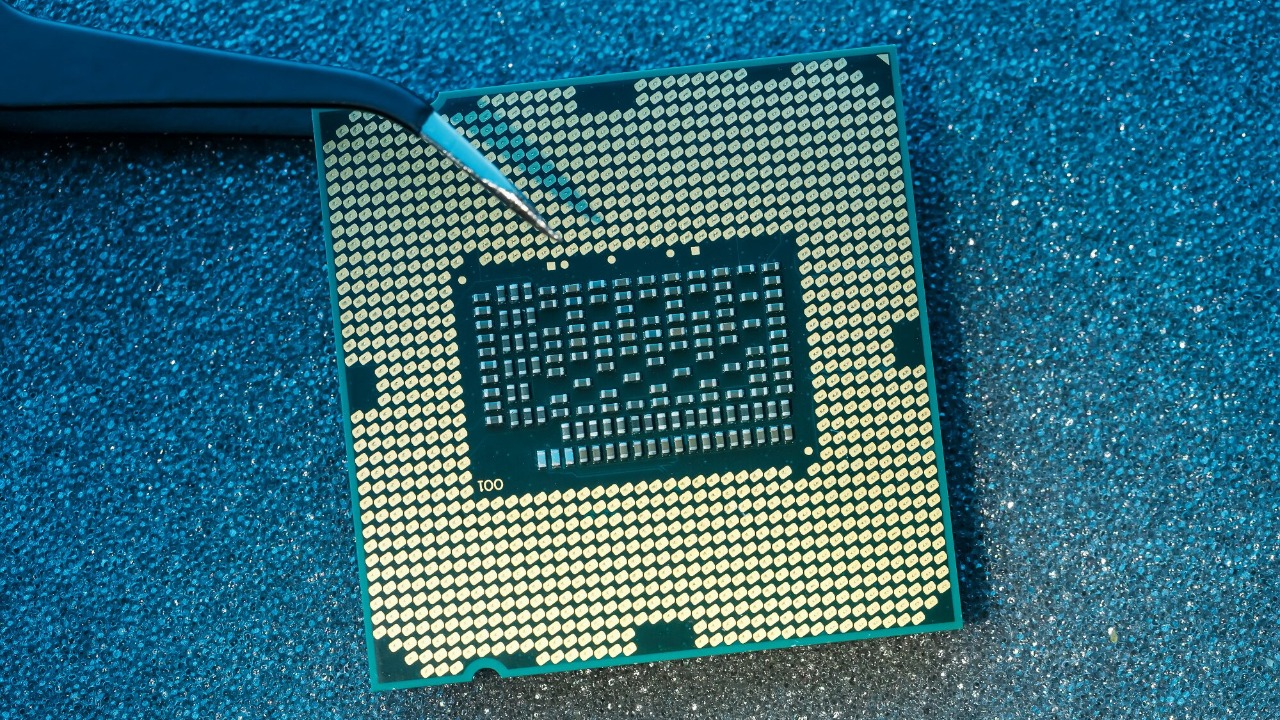

The core innovation in the new chip is a silicon-based architecture that minimizes decoherence in qubits by exerting precise control over electron spins inside a silicon substrate. Researchers structured the device so that individual electrons are confined in nanoscale regions, then manipulated with finely tuned electromagnetic pulses to perform quantum logic operations with far less noise than earlier designs. According to the team behind the most accurate quantum computing chip ever thanks to new silicon-based computing architecture, this approach allows qubits to maintain coherent quantum states long enough to complete complex gate sequences that would previously have been overwhelmed by errors.

Unlike superconducting or ion-trap systems that rely on exotic materials or elaborate vacuum and laser setups, the new chip is built using processes that are compatible with mainstream semiconductor manufacturing. The architecture embeds quantum functionality directly into silicon wafers that resemble those used in classical processors, which means the same foundries that fabricate advanced CPUs and GPUs could, in principle, produce large arrays of quantum devices. For stakeholders in cloud computing, finance, and high-performance computing, that compatibility signals a path toward integrating quantum accelerators alongside conventional chips on data center boards, rather than maintaining entirely separate, bespoke hardware stacks.

Embedding Quantum Dots For Ultra-Low Error Rates

At the heart of the design is a dense grid of quantum dots etched into the silicon, each dot acting as a controllable trap for a single electron whose spin encodes a qubit. Engineers arranged these quantum dots so that neighboring electrons can interact in a highly predictable way, enabling stable two-qubit gates with error rates below 0.1 percent. That sub-0.1 percent threshold is critical for fault-tolerant quantum computing, because it falls within the range where error-correcting codes can, in theory, suppress residual faults to arbitrarily low levels as the system scales. For companies exploring quantum-safe cryptography or large-scale optimization, such a low intrinsic error rate reduces the overhead needed for error correction and makes practical workloads more feasible.

The engineering feat lies not only in creating the quantum dots, but in wiring them up with control lines and readout circuitry that do not themselves introduce excessive noise. Researchers patterned metallic gates above the silicon to tune each quantum dot, while integrating sensitive charge sensors that can detect the spin state without collapsing the entire system. This tight integration of quantum dots, control electronics, and measurement hardware on a single silicon platform provides a template for future chips that could host thousands of qubits on one die, a scale that would be transformative for tasks like simulating complex molecules or optimizing global logistics networks.

Development Process and Challenges Overcome

The chip is the culmination of an iterative research program that began with simple silicon qubit prototypes and gradually advanced to multi-qubit arrays with increasingly sophisticated control. Early devices demonstrated that single electron spins in silicon could be initialized, manipulated, and read out, but they suffered from short coherence times and inconsistent gate performance. Over successive design cycles, the team refined the layout of quantum dots, improved the purity and isotopic composition of the silicon, and optimized the microwave control pulses, each step shaving down error rates and extending the duration over which qubits remained coherent.

One of the most stubborn hurdles involved suppressing noise in the silicon environment, including charge fluctuations and magnetic field variations that can scramble delicate spin states. Researchers tackled this by engineering cleaner interfaces between silicon and insulating layers, introducing shielding structures, and carefully filtering control signals to remove high-frequency interference. They also pushed the operating conditions toward what they describe as “room temperature approximations,” meaning the chip can maintain coherent quantum states at temperatures that are significantly higher than the millikelvin regimes required by many superconducting systems, even if full room-temperature operation remains a long-term goal. For hardware manufacturers and energy-conscious data center operators, the prospect of quantum devices that function at less extreme cryogenic conditions could dramatically cut infrastructure costs and simplify deployment.

Performance Metrics and Testing Results

In benchmarking experiments, the new silicon-based architecture delivered over 99.9 percent fidelity in single-qubit operations, a level that rivals or surpasses the best reported figures from competing platforms. Multi-qubit entangling gates, which are typically more error-prone, also achieved fidelities above 99.9 percent according to the research team, indicating that the architecture can sustain high-quality entanglement across the chip. These metrics were extracted from randomized benchmarking protocols and cross-checked with process tomography, giving independent confirmation that the reported numbers reflect genuine hardware performance rather than artifacts of a particular test.

To validate the chip under realistic workloads, the team ran error-corrected computations that stress the system over extended sequences of gates, rather than isolated operations. In these trials, the silicon architecture maintained a quantum advantage for longer durations than comparable superconducting or ion-trap devices, effectively delaying the point at which accumulated errors wash out the quantum signal. When compared with earlier generations of quantum chips, the researchers report a 50 percent improvement in overall error suppression, verified in controlled lab simulations that mimic the demands of algorithms used in chemistry, optimization, and machine learning. For users of quantum cloud services, such gains translate into the ability to run deeper circuits, explore larger problem instances, and obtain more reliable results from noisy intermediate-scale quantum hardware.

Implications for Quantum Computing Future

The emergence of a highly accurate, silicon-based quantum chip reshapes expectations for hybrid quantum-classical systems that pair specialized quantum processors with conventional CPUs and GPUs. Because the architecture is compatible with standard semiconductor fabrication, it opens the door to integrated packages where quantum and classical components share the same substrate or are stacked in three-dimensional assemblies. That kind of tight coupling would benefit industries like cryptography, where quantum accelerators could rapidly test candidate keys or analyze lattice-based schemes, and drug discovery, where quantum subroutines might evaluate molecular energy landscapes while classical code orchestrates large-scale simulations.

Looking ahead, the research team argues that the same design principles can be extended to arrays containing thousands of qubits, leveraging silicon’s suitability for mass production and the existing ecosystem of lithography, metrology, and packaging tools. If those projections hold, the cost per qubit could fall sharply as volumes rise, making quantum hardware more accessible to universities, startups, and enterprises that currently rely on remote access to a handful of experimental machines. For policymakers and investors, the shift from bespoke, laboratory-built devices to chips that roll off industrial fabrication lines would mark a turning point, signaling that quantum computing is moving from a speculative technology to a commercially viable platform with clear roadmaps for scaling, standardization, and long-term support.